# Fall 2003 - CSE 207 Digital Design Final Exam Review

## Numbers, Representation, and Arithmetic.

- (a) Represent the following decimal numbers as four-bit 2's-compliment numbers:

- i. 4 =

- ii. -3 =

- iii. −5 =

- (b) (3) Subtract 1110<sub>2</sub> from 0010<sub>2</sub> by adding the 2's complement of 1110<sub>2</sub> to 0010<sub>2</sub>

(c) (8) Using any technique generate the minimal sum of products. Box your final answer. You must show work for full credit.

| C | В | A | F |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

## **Sequential Circuit Design**

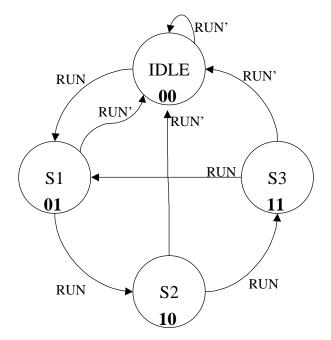

You are to design a circuit to implement the state transition diagram shown to the right.

This will be a Moore machine (outputs a function of the current state). It functions as follows: when RUN is true, the machine cycles through the states S1, S2, S3. As soon as RUN is false, the machine transfers to the idle state and waits there indefinitely. The system has the following outputs A, B, C. A it output when in state IDLE, S1, and S2. B is output when in state S2 and S3. C is output when in state S3 only.

a) Generate the truth table and excitation equations for the NextState  ${Q_1}^*\,{Q_0}^*$  given the CurrentState  ${Q_1}\,{Q_0}$  and the input RUN.

b) Generate the truth table and output equations A, B, and C given the CurrentState.

| Name:             | TA/Section:                                                                                                                                                                                                                                                                                                                                                                                     | Page 3 of 4                 |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|--|--|

| c)                | Draw the circuit showing all inputs and outputs.                                                                                                                                                                                                                                                                                                                                                |                             |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |  |

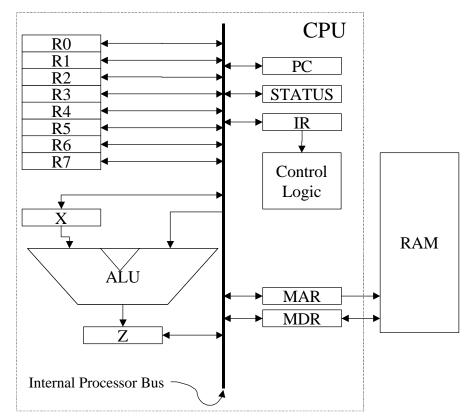

| Genera<br>need to | ement has decided that we need to implement the INC mem instruction as described in project te the register transfers and list all control signals necessary to implement this instruction. You worry about active-high or active-low – just indicate which control lines are asserted. All value are listed on the following sheet. You will start your microcode at the completion of Fetch ( | ou will not<br>alid control |  |  |  |

instruction is in the IR – what additional steps do you need to complete the execution of this instruction).

Name: \_\_\_\_\_ TA/Section: \_\_\_\_ Page 4 of 4

#### **Information:**

**Control Signals:**

PC\_INC, PC\_CLR, IR\_CLR,

ALU\_S3..0, ALU\_M, ALU\_Cin, C\_EN,

Z\_EN, Reset

R0..7\_OE, RX\_OE, RZ\_OE, MAR\_OE,

MDR\_OE, MDR\_MOE, IR\_OE,

PC\_OE, RAM\_OE

R0..7\_IE, RX\_IE, RZ\_IE, MAR\_IE,

MDR\_IE, MDR\_MIE, IR\_IE, PC\_IE,

RAM\_WE

## **Registers:**

R0, R1, R2, R3, R4, R5, R6, R7, RX, RZ, MAR, MDR, PC, STATUS, IR

### **Other Signals:**

IRdst, IRsrc, IRbits, RelAddr, ALUResult, RAM

#### ALU:

| ALU:        |           |                  |                             |                           |  |

|-------------|-----------|------------------|-----------------------------|---------------------------|--|

| Selection   |           | Active-High Data |                             |                           |  |

|             |           | M=H              | H M=L; ARITHMETIC FUNCTIONS |                           |  |

| S3 S2 S1 S0 | LOGIC     | Cn' = H          | Cn' = L                     |                           |  |

|             | FUNCTIONS | (no carry)       | (with carry)                |                           |  |

| L L         | L L       | F = A'           | F = A                       | F = A PLUS 1              |  |

| L L         | L H       | F = (A+B)'       | F = A + B                   | F = (A+B) PLUS 1          |  |

| L L         | H L       | F = A'B          | F = A+B'                    | F = (A+B') PLUS 1         |  |

| L L         | н н       | F = 0            | F = MINUS 1 (2's Cmp)       | F = ZERO                  |  |

| L H         | L L       | F = (AB)'        | F = A PLUS AB'              | F = A PLUS AB' PLUS 1     |  |

| L H         | L H       | F = B'           | F = (A+B) PLUS AB'          | F = (A+B) PUS AB' PLUS 1  |  |

| L H         | H L       | $F = A \oplus B$ | F = A MINUS B MINUS 1       | F = A MINUS B             |  |

| L H         | н н       | F = AB'          | F = AB' MINUS 1             | F = AB'                   |  |

| H L         | L L       | F = A' + B       | F = A PLUS AB               | F = A PLUS AB PLUS 1      |  |

| H L         | L H       | F = (A⊕B)'       | F = A PLUS B                | F = A PLUS B PLUS 1       |  |

| H L         | H L       | F = B            | F = (A+B') PLUS AB          | F = (A+B') PLUS AB PLUS 1 |  |

| H L         | н н       | F = AB           | F = AB MINUS 1              | F = AB                    |  |

| Н Н         | L L       | F = 1            | F = A                       | F = A PLUS A PLUS 1       |  |

| н н         | L H       | F = A+B'         | F = (A+B) PLUS A            | F = (A+B) PLUS A PLUS 1   |  |

| н н         | H L       | F = A+B          | F = (A+B') PLUS A           | F = (A+B') PLUS A PLUS 1  |  |

| Н Н         | Н Н       | F = A            | F = A MINUS 1               | F = A                     |  |